算力航母:英特尔展示 18A 工艺 AI 芯片,背面供电 + 垂直堆叠解决能耗瓶颈

英特尔代工服务本周发布了一份技术文档,展示了一款“AI芯片测试载具”,以验证其在先进封装领域的制造能力。测试载具是为验证制造工艺和设计思路而制造的工程样机,并非最终上市销售的产品。

根据技术文档,该测试载具的系统级封装拥有8倍光罩尺寸,内部集成了4个大型逻辑计算单元、12个HBM4级别的内存堆栈以及2个I/O单元。与上月展示的概念模型不同,本次展示的方案代表了英特尔目前已实际具备的量产制造能力。

在核心工艺方面,测试平台的核心逻辑单元采用了英特尔最先进的18A工艺,集成了RibbonFET全环绕栅极晶体管和PowerVia背面供电技术。在芯片互连方面,英特尔采用了EMIB-T 2.5D嵌入式桥接技术,通过在桥接器内部添加硅通孔,电力和信号不仅可以横向传输,还能实现垂直传输,从而最大化互连密度,设计支持高达32 GT/s的UCIe接口标准。

在芯片堆叠方面,英特尔将利用Foveros 3D封装技术(包括Foveros 2.5D、Foveros-R和Foveros Direct 3D)实现垂直堆叠芯粒。底层的18A-PT基础芯片位于计算芯片下方,可充当大容量缓存或处理额外任务。供电方面,英特尔将支持半集成电压调节器,并利用嵌入式同轴磁性电感器和多层电容网络,集成全套供电创新技术。与台积电CoWoS-L将电压调节器置于中介层不同,英特尔将其置于每个堆栈及封装下方,旨在应对生成式AI负载产生的瞬时电流波动,确保提供清洁、稳定的电力。

热点推送

-

蓝宝石发布黑钻、合金脉动 S 两款 RX 9060 XT 8G 显卡,2749 元起

蓝宝石今日推出了两款全新Radeon RX 9060 XT电竞显卡,分别是黑钻RX 9060 XT 8G D6 OC和合金脉动S RX 9060 XT 8G,售价分别为2999元和2749元

2026-02-28蓝宝石显卡,RX,9060 -

2026 国际冬季人工智能奥林匹克竞赛闭幕,中国和中国澳门代表队斩获两金一银

当地时间2月27日,2026国际冬季人工智能奥林匹克竞赛在斯洛文尼亚首都卢布尔雅那闭幕。中国和中国澳门代表队取得两金、一银和三项优胜奖的好成绩,主办方对中国选手的表现给予了高度评价和热烈祝贺

2026-02-28国际冬季人工智能奥林匹克竞赛,人工智能 -

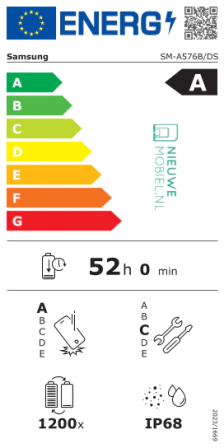

三星 Galaxy A37/A57 手机能效标签曝光:续航猛增,循环寿命调至 1200 次

科技媒体nieuwemobiel通过挖掘欧盟EPREL数据库,发现了三星Galaxy A37和Galaxy A57两款手机的能效标签。Galaxy A57的电池能效评级从B级提升至A级,理论续航时间也从44小时34分钟增加到52小时

2026-02-28Galaxy,A57,Exynos -

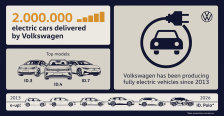

用时 13 年,大众品牌交付第 200 万辆纯电车型

大众品牌在电动化战略上取得了新的进展,其纯电动车型全球交付量正式突破200万辆。第200万辆新车为ID.3,产自大众茨维考工厂。 大众的电动化进程始于2013年,当时推出了e-up!,之后不断扩充纯电产品阵容

2026-02-28大众,新能源汽车 -

铁路部门继续实行预售期外学生预约购票常态化服务

铁路部门全力服务保障学生旅客出行,加强运输组织,优先分配票额,实行优惠票价,强化站车服务引导,较好地满足了学生旅客购票出行需求,助力平安有序返校。 继续实行预售期外学生预约购票常态化服务

2026-02-28中国铁路,12306 -

振华 LEADEX T1700W 钛金全模电源开售:双 12V-2x6 接口、140mm 双滚珠风扇,3999 元

振华现已为旗下LEADEX电源新增一款1700W版本(LEADEX T1700W),定价为3999元,提供十年质保

2026-02-28振华,LEADEX,T1700W -

曝 OpenAI 正向多家企业推介使用 ChatGPT 登录:可将 API 成本转嫁用户,无形扩大影响力

据报道,OpenAI 正在向多家企业推介“使用 ChatGPT 登录”功能。这一功能允许用户直接使用 ChatGPT 账号登录第三方网站,类似于“使用 Google 登录”或“使用 Apple 账号登录”

2026-02-28ChatGPT,OpenAI -

比亚迪腾势 N8L 汽车安全配置细节公布:9 个安全气囊、4 层热成型钢 A 柱,10 月 28 日上市

比亚迪腾势汽车官方发布了“腾势问答第七期”,解答了关于腾势N8L的相关问题,并公布了该车的安全配置细节。腾势N8L配备了9个安全气囊,A柱采用了4层热成型钢,支持高速爆胎不失控、高速紧急避让不怕侧翻、雨雪湿滑路面开得稳不打滑等特性

2026-02-28比亚迪,腾势,N8L -

realme 真我 GT8 Pro 搭载全腔对称式双 1115E 大师级扬声器,号称低音音质表现最好的手机之一

真我手机官方近日继续预热旗下GT8 Pro旗舰新机。这款手机采用双1115E全腔扬声器结构,搭载0816瑞声顶级马达,并通过了IP69、IP68和IP66三重认证。此外,该机还配备了超声波指纹解锁功能,支持n79频段及全球21个5G频段

2026-02-28真我,GT8,Pro -

英伟达 CEO 黄仁勋将出席亚太经合组织 CEO 峰会,计划与全球领导人和韩企高管见面

美国人工智能芯片制造商英伟达宣布,公司首席执行官黄仁勋将于本月出席在韩国举行的亚太经合组织企业领袖峰会,并计划与全球领导人及韩国顶尖企业高管会面

2026-02-28黄仁勋,英伟达,APEC峰会 -

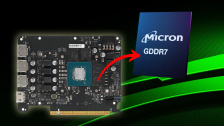

首搭美光 GDDR7 显存,影驰 RTX 5060 显卡拆解曝光

持续的 DRAM 短缺严重影响了硬件市场。最新迹象显示,英伟达正试图拓展更多存储芯片供应商

2026-02-28影驰,RTX,5060 -

俄罗斯联邦通信监督局称其官网及国防部网站遭 DDoS 网络攻击

据报道,俄罗斯联邦通信、信息技术和大众传媒监督局表示,其官网以及俄罗斯国防部的网络资源正在遭受分布式拒绝服务攻击

2026-02-28俄罗斯国防部,DDoS,网络攻击 -

HMD 推出 4G 新机 Luma:紫光展锐 T615 处理器、3.5mm 耳机孔、SD 卡槽

HMD推出了一款名为Luma的新款智能手机。这款手机搭载了紫光展锐T615处理器,基于12nm工艺,采用Cortex-A75和Cortex-A55核心架构

2026-02-28hmd -

ChatGPT 成人模式“Naughty Chat”代码现身新版客户端,需进行身份验证

AI聊天机器人正逐渐改变人们的生活。随着技术的进步,这些工具不仅能够处理日常事务,还开始满足用户的情感需求,许多人将ChatGPT等工具视为挚友或恋爱对象。最近,OpenAI下架了GPT-4o模型,引起了部分用户的不满

2026-02-28ChatGPT,OpenAI,萨姆 -

疑似 Vision GT 概念超跑现身后,小米宣布 MWC 2026 还有 One more thing

北京时间2月27日晚间,小米通过官方X账号宣布,在西班牙当地时间2月28日14时的发布会上将有“One more thing”。该账号还发布了一张形似汽车轮廓的预告图

2026-02-28小米汽车,MWC,2026 -

英特尔发布 8531 Game On 显卡驱动,支持《生化危机:安魂曲》等游戏

英特尔发布了32.0.101.8531版本的Arc锐炫显卡Windows驱动程序。这个版本属于Game On系列,新增了对《生化危机:安魂曲》《失落星船:马拉松》两部新作以及《魔兽世界:至暗之夜》DLC的支持

2026-02-27英特尔,显卡驱动 -

Stellantis 去年首次亏损,CEO 菲洛萨坦言高估了能源转型速度

Stellantis 集团于2月26日公布了2025年的全年财务业绩。集团实现净营收1535亿欧元,较2024年下降2%,主要原因是汇率问题及上半年产品净价下滑带来的负面影响

2026-02-27Stellantis -

Aliro 1.0 智能门禁标准亮相:苹果、谷歌、三星等支持,让 iPhone 17 等手机变“万能钥匙”

连接标准联盟(CSA)于2月26日发布了Aliro 1.0智能门禁标准,得到了苹果、谷歌和三星等科技巨头的支持。该标准旨在打破硬件生态壁垒,使门禁系统能够无缝连接智能手机、可穿戴设备等

2026-02-27Apple,Watch,iPhone -

Figma 升级支持 Codex 对接,代码与设计画布实现互联互通

Figma 宣布推出 Codex 对接功能,团队可以将实际运行的真实界面同步到 Figma 中,共同探索设计方案、打磨产品细节并做出决策。优化后的内容可以回传至 Codex 平台,同时保留设计上下文

2026-02-27Figma,Codex -

中国气象局发布 2025 年热门气象数据开放共享目录,涉及地面、高空、卫星等

2月26日,中国气象局发布了2025年热门气象数据开放共享目录,展示了全年下载量较高的地面、高空、卫星、海洋、实况及再分析等气象数据和产品

2026-02-27中国气象局 -

Sonos 2026 年将再度改版移动应用程序:关注用户反馈,简化使用操作

Sonos 向彭博社透露,今年将再次对移动端应用程序进行改版升级。在吸取2024年新版App失败的经验后,这次公司会优先考虑用户反馈,不会急于全面开放

2026-02-27Sonos -

首台量产车刚下线没多久,特斯拉 Cybercab 项目经理维克托 · 内基塔离职

特斯拉Cybercab项目经理维克托·内基塔宣布离职,而就在不久前的2月18日,Cybercab首台量产车在得克萨斯超级工厂下线

2026-02-27特斯拉,Cybercab -

HKC 推出“战狼 V5”23.8 英寸显示器:1080P 180Hz,499 元

HKC在京东上架了一款名为“战狼 V5”的23.8英寸显示器,主打1080P 180Hz刷新率,售价499元

2026-02-27HKC -

京瓷在日本推出 au TORQUE G07 三防手机:可拆卸电池、IPX6/IPX8/IPX9 防水 + IP6X 防尘认证

京瓷在日本市场联合运营商au推出了一款TORQUE G07手机。这款手机造型坚固,主打三防体验,具备IPX6/IPX8/IPX9防水认证和IP6X防尘认证,并且支持更换电池

2026-02-27手机,京瓷 -

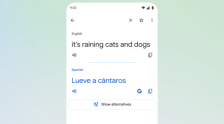

谷歌翻译引入 Gemini AI 功能,提供同义替换及语境信息

谷歌翻译近日宣布推出全新的AI功能升级,旨在帮助用户更好地理解翻译内容中的语境信息。这次更新得益于Gemini强大的多语言能力,现在谷歌翻译可以提供实用的同义替换表达,尤其在处理习语和口语化短语时更为有效

2026-02-27Gemini,谷歌翻译 -

英特尔 Arc 显卡 32.0.101.8531 驱动发布,适配《失落星船: 马拉松》等新游戏

英特尔为旗下Arc显卡发布了32.0.101.8531驱动程序(Beta版),适用于Windows 10 22H2和Windows 11 21H2及以上系统,文件大小为1.3GB

2026-02-27英特尔,Arc,显卡 -

三年三裁:eBay 宣布将裁减约 6% 全职员工,波及约 800 人

今天晚间,据彭博社报道,eBay 宣布将裁员约 800 人,占全职员工总数约 6%,以配合公司的战略重点。公司正在重新配置资源并优化组织架构,因此部分岗位将受到影响。eBay 将为受裁员影响的员工提供必要支持,并继续在关键业务领域招聘人才

2026-02-27ebay -

折痕几乎看不见:荣耀王飞晒 Magic V6 内屏,称折叠屏前提应是不妥协的轻薄

荣耀工作人员王飞近日分享了关于Magic V6折叠屏手机内屏的情况。他强调,良好的折痕控制对于吸引初次使用折叠屏或对折叠屏仍有顾虑的用户非常重要。王飞还指出,折叠屏手机不能仅仅依赖于折痕处理得好,而应追求不妥协的轻薄设计

2026-02-27骁龙,8,至尊版 -

谷歌推出 Nano Banana 2 图像 AI 模型:支持 4K 分辨率输出、改进中文字符乱码问题

谷歌正式发布了Nano Banana 2图像模型。该模型基于Gemini 3.1 Flash Image构建,相比上一代版本,响应速度更快,理解能力更强,对用户提示词的解析也更加精准

2026-02-27谷歌,Nano,Banana -

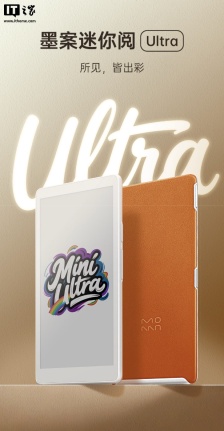

墨案迷你阅 Ultra 彩色墨水屏阅读器发布:手机造型、145g 重量,2399 元

墨案推出了一款迷你阅 Ultra 手机造型彩色墨水屏阅读器,售价为 2399 元。这款阅读器整体尺寸为 161.5 x 80 x 7.7mm,重量为 145g,正面采用白色边框设计

2026-02-26迷你阅,Ultra,墨案